The TTPController is an integrated CMOS device which implements the functionalities and features of the SAE AS6003 standard established back in 2011. It is designed using our DO 254-compliant C2NF chip IP and is commercially available in its third generation. Its datasheet is available in the Downloads section below.

Application fields

Standard TTP® controllers are commercially available from TTTECH since 1999. Although the open TTP standard was not developed for a specific application field, it clearly targets safety-critical applications due to built-in redundancy and fault-tolerance mechanisms as well as the development guidelines followed. Main use is in aviation (see press release) for modular/distributed real-time control systems. See our case studies for Honeywell MAC and the Boeing 787 Dreamliner. The TTP controller is also used in fly-by-wire systems on the Bombardier Global 7500/8000, Embraer Legacy and Praetor, and the Airbus A220."

Certified off-the-shelf communication controller

The TTP chip IP and supporting embedded software were designed to meet the stringent requirements of RTCA DO-254 / EUROCAE ED-80 and DO-178B up to the highest Design Assurance Level (DAL A) and got certified in a long list of projects. TTTECH supports new projects with certification data packages and highly experienced engineers.

Downloads

Key benefits

- Dual-channel TTP controller for deterministic, collision-free, redundant data transfers at data rates of up to 20 Mbit/s

- Bus interface (speed, encoding) selectable independently for each channel

- Certification data package according to RTCA/DO-254 DAL A available

- Perfectly suited for dependable distributed real-time systems with guaranteed response times

- 40 MHz main clock and 16 MHz bus guardian clock

- Single 3.3V power supply

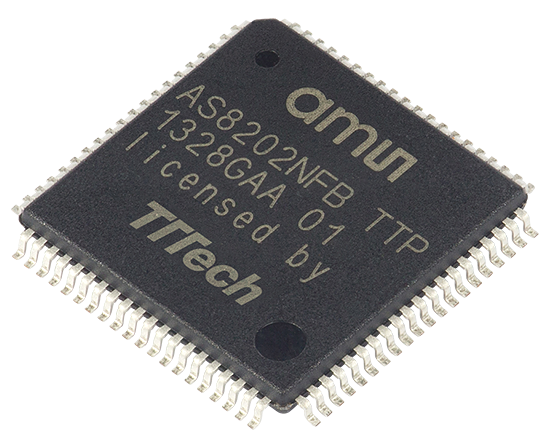

- 80 pin LQFP80 package

- Operating temperature range from -40ºC to 125ºC

- 16k x 16 SRAM for message, status, control area (communication network interface) and for scheduling information (MEDL)

- 4k x 16 (plus parity) instruction code RAM for protocol execution code

- Software tools, design support and development boards available

- RoHS compliant

Application notes

Application notes are available on request and in our Customer Portal